M5Stack用FPGAボードに搭載しているMAX Vシリーズには、オシレータが内蔵されています。(ので、外部発振回路を設けていません。)

FPGAのテストとして、内蔵オシレータを動かしてみます。

プロジェクト作成からの手順は、以下の通り。

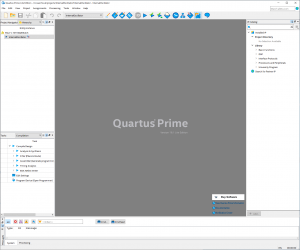

- Quartus Primeを起動

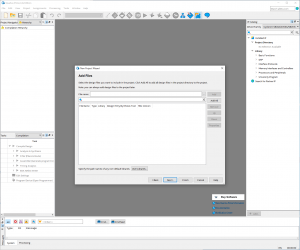

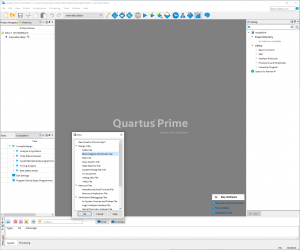

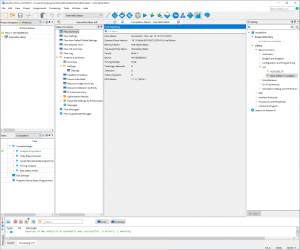

- File-New Project Wizardを実行

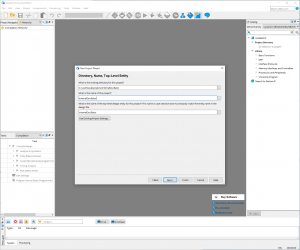

- プロジェクトを作成するディレクトリ名、プロジェクト名、デザインファイル名を入力(すべて、「InternalOscillator」としています)

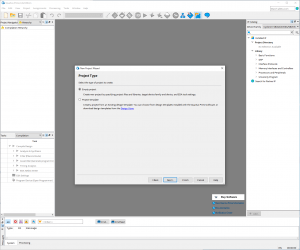

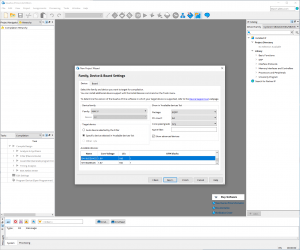

- Nextをクリックして「Fammily, Device & Board Settings」まで進め、実装したデバイス「5M160ZE64C5」を選択

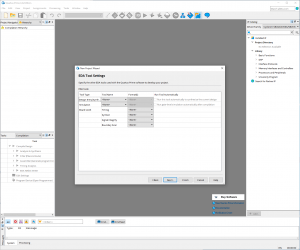

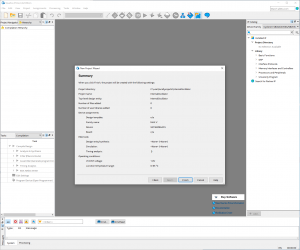

- Nextをクリックして「Summary」まで進めて、Finish

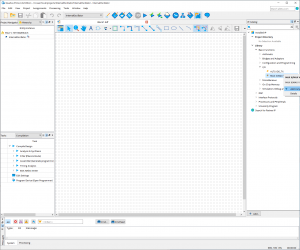

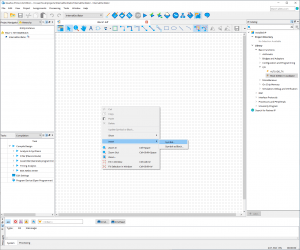

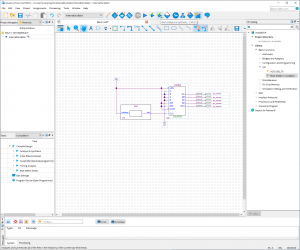

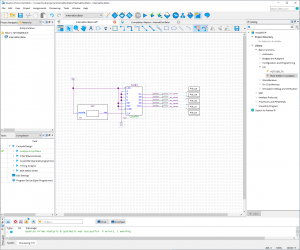

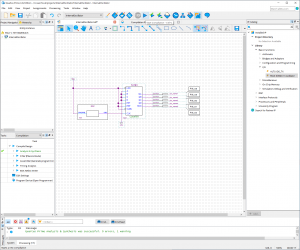

- File-Newで、「Block Diagram/Schematic File」を選択

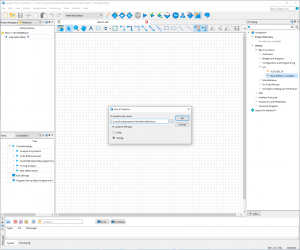

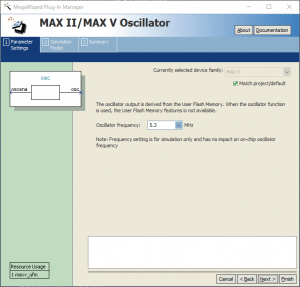

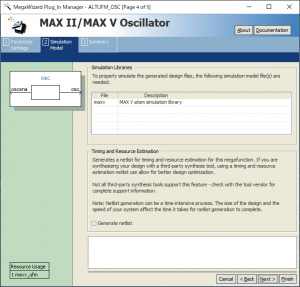

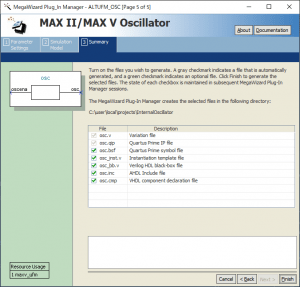

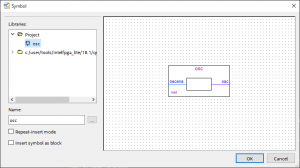

- 右側の「IP Catalog」の「MAX II/MAX V oscillator」で右クリック、オシレータを作成してファイル保存(発振周波数は、5.3MHzとしました)

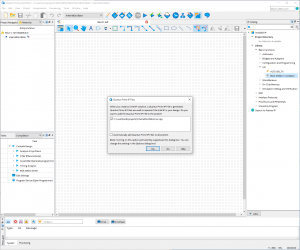

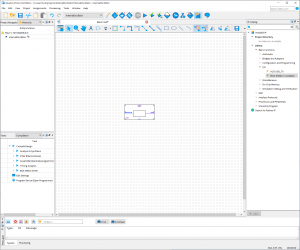

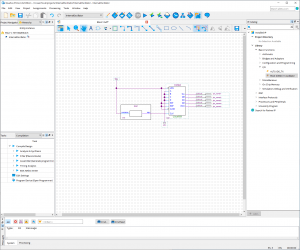

- 作成したオシレータとその他(カウンタ、GND、VCC、出力ピン)を回路図上に配置(カウンタ74163のRCO、QD、QC、QB、QAの5端子を出力ピンにつないでいます)

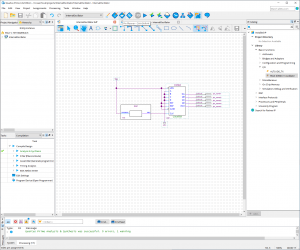

- 「Start Analysis & Synthesis」を実行(左下の「Task」で実行結果を確認。失敗するようなら、回路の接続を再確認します)

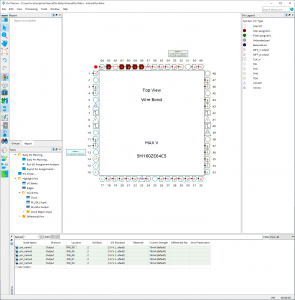

- 「Pin Planner」を実行し、出力ピンをデバイスのピンに割り当て(RCOを63、QDを61、QCを60、QBを59、QAを58)

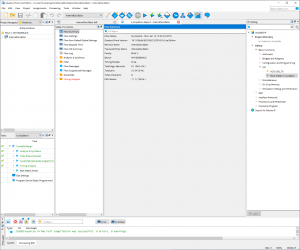

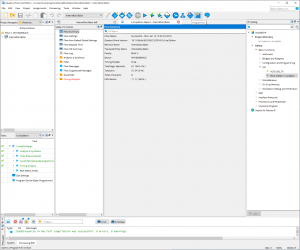

- 「Start Compilation」を実行(左下の「Task」で実行結果を確認)

- ここで、PCとUSB Blaster、FPGAボードを接続

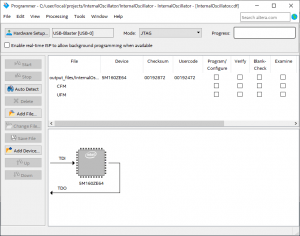

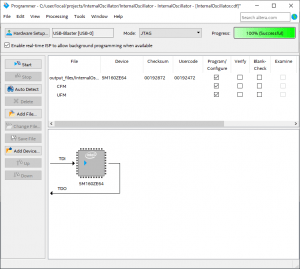

- 「Programmer」を実行(接続確認を兼ねて「Auto Detect」でデバイスを認識させます)

- 「Program/Configure」にチェックを入れ、「Start」を実行(右上のProgressが「100%(Successful)」となればOK)

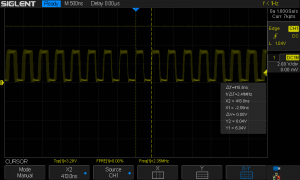

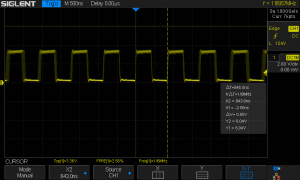

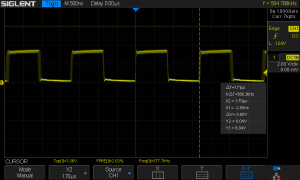

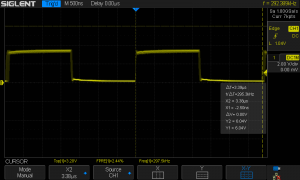

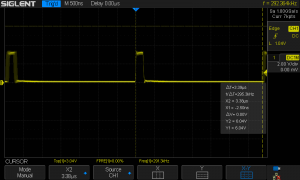

- ここまででFPGAへの書き込みは完了しているので、出力ピンを波形観測(上から順に、QA、QB、QC、QD、RCO)

原発振は5.3MHzとのことでしたが、QAが2.41MHzとなっているので実際は4.8MHzといったところでしょうか。ジッタも結構あります。

高精度なクロック発振を求められるアプリケーションには向きませんが、簡易な装置向けとしてはアリなんじゃないでしょうか。